# PROCEEDINGS OF SPIE

SPIEDigitalLibrary.org/conference-proceedings-of-spie

Rank differences of signals by weighing-selection processing method for implementation of multifunctional image processing processor

Vladimir G. Krasilenko, Alexander A. Lazarev, Diana V. Nikitovich

Vladimir G. Krasilenko, Alexander A. Lazarev, Diana V. Nikitovich, "Rank differences of signals by weighing-selection processing method for implementation of multifunctional image processing processor," Proc. SPIE 11163, Emerging Imaging and Sensing Technologies for Security and Defence IV, 111630J (16 October 2019); doi: 10.1117/12.2538493

Event: SPIE Security + Defence, 2019, Strasbourg, France

# Rank differences of signals by weighing-selection processing method for implementation of multifunctional image processing processor

Vladimir G. Krasilenko\*<sup>a</sup>, Alexander A. Lazarev<sup>b</sup>, Diana V. Nikitovich<sup>b</sup>

<sup>a</sup>Vinnitsa Social Economy Institute, 86/131 Kelestskaya Str., 21021, Vinnitsa, Ukraine;

<sup>b</sup>Vinnitsa National Technical University, Ukraine.

# **ABSTRACT**

In this paper, we proposed a new iterative process of sorting an array of signals, which differs from the known structures of sorting signals by uniformity, versatility, which allows direct and inverse sorting of an array of analog or digital signals. The basic elements of the proposed sorting structures are simple relational nodes. Such elements can be implemented on a different element basis, including, on devices for selecting a maximum or minimum of two analog or digital signals, which are implemented on CMOS current mirrors and carry out the limited difference function of continuous logic. We offered implementation of homogeneous sorting structure on such elements, consisting of two layers and a multichannel sampling and holding device. Nine signals corresponding to a selection window of a matrix sensor are fed to this structure, we sort them in five iterative steps, and at the output we receive the signals sorted by the rank, which, using the code controlled programmable multiplexer, generates an output signal, corresponding to the selected rank. We evaluated the technical parameters of such a relational preprocessor. The base cells consist of no more than 20 CMOS 1.5 µm transistors, the total power consumption of the sorting node on 10 continuously logical base cells (CL BC) is 2mW, the supply voltage is 1.8÷3.3V, the range of an input photocurrent is 0.1÷24μA, the conversion cycle is 10us. The paper considers results of design and modeling of CL BC based on current mirrors (CM) for creating picture type image processors (IP) with matrix parallel inputs-outputs. Such sorting nodes based on them have a number of advantages: high speed and reliability, simplicity, small power consumption, high integration level. The inclusion of an iterative node for sorting signals into a modified nonlinear IP structure makes it possible to significantly simplify its design and increase the functional capabilities of such processor. The simulation results confirm the proposed approaches to the design of sorting nodes of analog signals of the iterative type, which simplify the complexity of the nodes by an order of magnitude, ensuring their uniformity, regularity and simplicity of scaling. The power consumption of the processors does not exceed 2mW, the response and processing times are 10µs and can be less by an order of magnitude, the supply voltage is 1.8÷3.3V, and the operating currents are optimally in the range of 10÷20μA. The energy efficiency of the proposed preprocessor with the iterative sorting node is  $25 \times 10^9$  op / s · W, which corresponds to the best technical solutions. In the work we are shown, that after sorting or comparative analysis of signals by levels of selected window of image, a promising opportunity appears to implement image processors with enhanced functionality using the new method of weighting-selecting rank differences of signals. The essence of the method is that by composing the differences of the signals ordered by rank and the upper level of their range, we can simultaneously form several resulting output signals, choosing the necessary difference signals from their set according to the control commands and weighing them additionally before the summation. We are shown that using this approach and the method of processing the current window signals significantly expands the set of operations and functions for filtering images, simplifying hardware implementation of IP, especially for analog and mixed technologies. We determined set of basic possible executable instruction-functions by processors based on such a proposed method, presenting the simulation results in Mathcad, PSpice OrCad and other environments. We discussed the comparative evaluation of various modifications and options for implementing processor. We analyzed the new approach for the programmable choice of its function or set of functions, including the choice of the required differences between the ranks of signals and their weights. We show the results of design and modeling the proposed new FPGA-implementations of MIP. Simulation results show that processing time in such circuits does not exceed 25 nanoseconds. Circuits are simple, have low supply voltage (2.5 V), low power consumption (50mW), digital accuracy. Calculations show that when using an Altera FPGA chip EP3C16F484 Cyclone III family, it is possible to implement MIP with register memory for image size of 64\*64 and window 3\*3 in the one chip. For the chip for 2.5V and clock frequency 200MHz the power consumption will be at the level of 200mW, and the calculation time for pixel of filters will be at the level of 25ns.

**Keywords:** analog relational preprocessor, image nonlinear processing, simulation, continuous logic, current mirror, sorting networks, methods of selection and rank preprocessing, rank filtering.

Emerging Imaging and Sensing Technologies for Security and Defence IV, edited by Gerald S. Buller, Richard C. Hollins, Robert A. Lamb, Martin Laurenzis, Proc. of SPIE Vol. 11163, 111630J © 2019 SPIE · CCC code: 0277-786X/19/\$21 · doi: 10.1117/12.2538493

<sup>\*</sup> krasvg@i.ua

# 1. INTRODUCTION

Intelligent optical detectors based on photodiodes or intelligent optical sensors that can be seamlessly integrated with digital electronics in silicon, which greatly simplifies the design of OE-VLSI circuits and allows you to implement a stacked architecture of a three-dimensional chip, demonstrate a large scope and market potential<sup>1-3</sup>. Since smart detector circuits can be made from almost any semiconductor fabric <sup>1-2</sup>, and many demonstration systems have already been created to prove the use of optics or optoelectronics for external and internal microcircuits, our approach prefers an intelligent pixel-like architecture<sup>3-13</sup>. that combines parallel signal detection with parallel processing signals in one circuit, when each pixel has its own analog and analog-to-digital node, which guarantees the fastest processing. Parallel high-speed processing of a 1D or 2-D array using non-traditional MIMO systems, the corresponding matrix logics (multi-valued, continuous, neural-fuzzy and others) and the corresponding mathematical apparatus becomes a strategic direction 4-23. By the variety and scope of applications in the most diverse areas of science and technology, not to mention information technology, Boolean two-digit logic covers the entire binary-discrete (virtual) world and therefore the 20th century can rightly be called Boolean. But in the overwhelming majority of cases, various production processes and technologies of the physical macro-world, especially technologies associated with measurement and control processes, are accompanied not by discrete, but by accompanying continual (continuous analog) processes and signals, which leads to contradictions in the use of discrete logics in the continuum<sup>14</sup>. Therefore, for the description and modeling of each continual subject domain and the class of its tasks, its own logical-algebraic apparatus is required. Logic-algebraic (LA) calculi are mathematical (symbolic) domain-oriented logics and special algebras, the formal apparatus of which is based on clear rules that allow you to make an exact description of a certain class of problems and even suggest an algorithm for solving them. For the successful development of continual information technologies and artificial intelligence 15, 16 it is necessary to increase the semantic power of LA-calculus. And for this, both philosophically and mathematically, it is necessary to define their new basic definitions, concepts and, at least on an intuitive level, using them to describe and model the machine-mechanical analogs of thinking processes<sup>17</sup>. The basis of information technologies in the analog field is precisely the continual LA calculus: Lukasiewicz's infinite-valued logic<sup>18</sup>, continuous logic with all its variants and generalizations<sup>19, 20</sup>, additive-multiplicative logic (AM) algebra<sup>21</sup>, predicate selection algebra<sup>22</sup>, equivalence algebra<sup>23</sup> and others. They determined the continual biologically inspired stage of development of LA-calculus and a new, more energy-efficient, direction of building models and their hardware implementations of artificial intelligence. Many logics are based on multi-place, multi-input mini-max operations: min  $(x_1, x_2, \dots, x_n)$  and max  $(x_1, x_2, \dots, x_n)$ , when defining variables on a unit interval<sup>19, 20</sup>:  $x_i \in [0,1]$ . Note that many models and image processing algorithms, artificial neuralfuzzy systems, their basic procedures of composition-decomposition and fuzzy inference are also based on such multiinput mini-max operations. Therefore, there is an urgent need to improve the hardware implementations of nodes that perform these and similar operations, especially for those applications where the number of operations and input variables are significant. Arrays of matrix elements of continuous and threshold, rank, and order logic are also required for promising implementations of future computing architectures based on 3D chips, including optical training neural networks (NN) with a two-dimensional structure<sup>4</sup>, equivalence models (CLEM) NN<sup>5+7</sup>, especially to create convolutional and new self-learning equivalence-convolutional structures<sup>24-27</sup>. The use of architectures with time-pulse-coded analog variables (TPCA), which were considered in works<sup>6, 7, 8, 10, 12</sup> and based on a generalized unified methodological basis for creating a whole family of universal (multifunctional) elements of various logics, although they provide many advantages regarding the expansion of the set of functions and their programmable samples do not satisfy the time requirements while maintaining a satisfactory dynamic range in terms of accuracy. Such a time-pulse-encoded representation of matrix continuous logic variables by two-level signals, although it allows you to expand the functionality and simplify the tuning circuit for the required function, does not satisfy the increased requirements for speed and accuracy of calculations. In works<sup>7, 8, 11, 12</sup> the fundamentals of designing universal (multifunctional) logic elements (ULE) of a matrix logical structure with fast programmable tuning were considered. Consider a brief overview, the motivation for designing a multifunctional image processing processor. A special place among the methods of effective high-speed image processing working with arrays is occupied by the class of structured nonlinear methods and algorithms that performed the conversion of the form:

$$\mathbf{B} = \{b_{ke}\} = \mathbf{F}(\mathbf{A}) = \{\mathbf{\Phi}_{\kappa l}(\mathbf{A}_{\kappa l})\},\$$

where  $\Phi_{\kappa l}(A_{\kappa l})$  — nonlinear function which is determined by subset of rank and (or) index statistician of selection. It is formed by signal samples from some neighboring of this element in the sequence of the well-organized samples of signal, and it is named as variational series<sup>28</sup>. By virtue of the last this subclass was adopted by rank algorithms. The algorithms of extreme filtration, using values of minimum and maximum on samples of neighborhood space, are the special cases of the rank algorithms. Any r-th index statisticians  $v_s(\mathbf{r})$  of display (k, l) the set neighboring of which form

other  $(N_s-1)$  the elements of selection it is possible to bind to the local histograms of distributing of values of neighboring elements and with the proper functions of the well-organized choice  $F_n^m \vec{x}$  ( $\vec{x}$ ) element, where  $\vec{x} = (x_1, x_2, ..., x_n)$ . Such functions at any values of changing variables choose that size which at the location all right not decreasing are occupied by m-th place. These functions can be represented by a logical formula <sup>19</sup>:

$$F_n^m(x) = \max[\min(Xi_{1,...}Xi_{n-m+1})], \quad \text{or } f^{(r)}(x_1,...,x_n) = x^{(r)}, r = \overline{1,n},$$

where r-rank of the base operations of continuous logic (CL)<sup>20</sup>. Index operations are used with operations of denial, addition. Thus for r = n this operation passes to n-local disjunction, for r=1 to n-local conjunction. As examples of functions of ordinal logic can be the median and inversion of the median, as well as a number of others<sup>20</sup>. The algebra formed in a number of C = [0, 1] with base operations f(r) and (-) is named ordering Boolean algebra. The row of specific laws is inherent to it: tautology, commutative, distributive 20. Rank algorithms are locally-adaptive on the same essence: simplicity of local adaptation, invariance to spatial links and to signals dimension, almost algorithms complication independence from the sizes of neighboring. Also, at calculation of concrete rank statistician and derivative the further simplifications related to informative surplus of images are possible. In paper<sup>29</sup> approaches to creation of classifiers of the distributed ensembles of continuous signals were shown. The distributions of their amplitudes were used to evaluate the characteristics of classified objects and classifiers that control and compare the correlations of the so-called lattice functions based on a hierarchical description of the shape. Such descriptions in terms of more than or equal to, less than or equal to, or in terms of more, less, and the same, also require the use of similar operations of order logic and the like. The proposed models of neuron classifiers and identification algorithms based on a hierarchical description of the forms of lattice functions allow one to theoretically quite subtly isolate and compare these forms. Estimates of the number of potentially distinguished forms show that such multilayer neural recognizer classifiers with n inputs and (n-2) layers (according to classification levels) can have high accuracy of multilayer classification. Thus, analysis of foregoing allows drawing conclusion about the necessity of development of hardware sorting devices with the sufficient number of inputs (executing «ordering» of input values and supervisory after the well-organized locations (variables). Taking to account that at the proper transpositions, the common number of combinations of all links is very great, clearly that the use of new technologies is the decision of problem. Known base cells, that forms such converterorders<sup>29</sup>. They are executed as association of two logical charts: charts of selecting of a less value min(x1, x2) and charts of function max(x1, x2). Also well-known wave structures that are completely homogeneous with regular connections are based on such basic cells that order the ranking of the analog or digital variables<sup>29</sup>. The continuously logical (CL) – transformations are shown in paper<sup>30, 31</sup>, in which the transformation CL functions (CLF) are defined and it is shown that the operation of min, max of continuous logic are the basic operations of the functions. Use of operators of hybrid logic for formation of CLF it is possible:  $D_1[P(x1,x2)] = \max(x_1,x_2)$ ,  $D_2[P(x1,x2)] = \min(x_1,x_2)$ , where P and D are respectively the threshold and the de-threshold operators, which are realized by various means. Besides, in works<sup>30,31</sup> it has been shown that some operations of continuous logic, such as equivalence and nonequivalence, and their generalized family, allow to receive a number of advantages in so identified «equivalence to a paradigm» neural-network models. These scalar operations of equivalence eq (x, y) and nonequivalence neq (x, y) for  $x, y \in [0,1]$  are defined in works<sup>6,7,</sup> namely: eq  $(x, y) = x\Lambda y + \overline{x}\Lambda \overline{y} = \min(x, y) + \min((1 - x), (1 - y)) = 1 - |x - y|, \text{ neq}(x, y) = |x - y| = 1 - \text{eq}(x, y) = 1$  $= \max(x, y) - \min(x, y) = \max(\overline{x}, \overline{y}) - \min(\overline{x}, \overline{y}) = (x - y) + (y - x)$ , where (-) is the operation of a limited difference. If we consider that at  $y = 1 - x = \overline{x}$ , these functions are transformed to: eq  $(x, \overline{x}) = 2(x \wedge \overline{x}) = 2\min(x, \overline{x})$ ,  $\operatorname{neg}(x, \overline{X}) = \max(x, \overline{X}) - \min(x, \overline{X}) = 1 - 2\min(x, \overline{X})$ , as has been shown in work<sup>30</sup>, these functions can be successfully used in CL ADC. The use of CL-transformations and CLF made it possible to create promising energy-efficient analog-todigital converters for intelligent detectors on their basis 30, 31, 32. In many neural-network models for recognition of gray images it is desirable to have picture binary bit-planes, which encode the image matrix in Gray codes. And for this, the CL-ADC with the Gray code is suitable. In realization of equivalence models<sup>3, 5, 23</sup> and scalar-relation processors<sup>10</sup> in every channel it is necessary to realize component-wise equivalence operations of type:  $a_i \stackrel{\checkmark}{\sim} b_i$  and other types for which the maximum and minimum values or their differences are required. They also require of variables ranging  $a_{i}$ ,  $a_{i}$ ,  $b_{i}$ , represented by optical signals and will realize min and max operations on from 2 to 4 variables. But the implementation of such continuously logical base cells (CL\_BCs), which perform the operations min (x1, x2) and max (x1, x2), is rather complicated for digital variables<sup>19</sup>. And the CL BC based on current mirrors (CMs), proposed in work<sup>30</sup>, although simple, only 13 CMOS transistors, their number to build a traditional know wave network structure of such cells, especially at large values ( $n \approx 9 \div 25$ ), is very large. At the same time, an increase in the depth of the structure, the number of layers of CL BCs, all the same increases both the complexity and the sorting time. But at the same time with an increase in the number of analog cells accuracy decreases, so more accurate digital implementations need to be sought.

To create fully parallel algorithms and tools for image processors<sup>31, 32, 33</sup> morphological image processing<sup>34-37</sup>, especially for implementing such basic operations as dilation, erosion, opening, closing<sup>37</sup>, etc., the above mentioned min-max operations on sets of signals are also necessary, which represent structural windows or selected fragments processed images. Many of the above-mentioned morphological operations need to be repeated many times and for all the current fragments of the image being processed, therefore, there is an urgent need to reduce the execution time and the underlying min-max operations and ranking operations. Sorting algorithms have been widely researched due to the need for sorting in many applications <sup>38-41</sup>. Sorting algorithms have been specialized for particular sorting situations, such as, high-speed sorting <sup>42</sup>, sorting using a single CPU and multiple CPUs, parallel image and big data processing 43. To create more advanced intelligent sensors and image processing processors 32,33 with enhanced functionality and combining analog or analog-digital preprocessing of signals in a dedicated and accessible structural area (window) also requires sampling, storage, sorting and selection of signals. In papers 44, 45 approaches to creation of programmable relational optoelectronic time-pulse coded processors as base elements for sorting neural networks were shown. But in such a relational optoelectronic processor, working with analog signals both amplitude-coded and time-pulse-coded, the sorting structure for ordering signals is complex, since the number of base cells in the layer and the required number of layers increase proportionally with the number of input variables. Therefore, the goal of our work is to search for compromise new options for implementing both signal sorting nodes, including analog and digital, providing increased accuracy and speed, and based on them relational non-linear image processing processors with advanced functionality. And since such processors can be used as multifunctional nodes of ordinal logic, extremum selectors, nodes of ordering and sorting data, rank filters, recognizers of fragment classifiers, etc., the question of their implementation is acute. In addition, taking into account the recent emergence of a new element base, our task is to prove the possibility of creating on the FPGA, practically in one chip, an image preprocessor (IP) with enhanced technical characteristics and a wide range of commands through the use of a new method of processing pre-ranked signals and (or) their differences. Therefore, the goal of our work is the design and modeling of technical options for the implementation of the main nodes, including the sorting nodes, which significantly expand the functionality and range of tasks solved by multifunctional relational image preprocessors.

# 2. STRUCTURE DESIGN OF NONLINEAR PROCESSING RELATIONAL PREPROCESSOR BASED ON SORTING NODE

## 2.1 Structure of the basic relational preprocessor (BRP) of nonlinear image processing

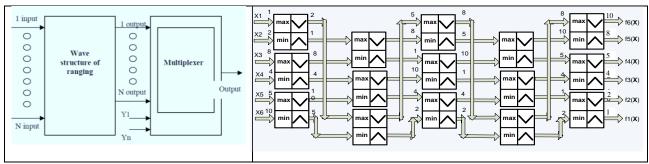

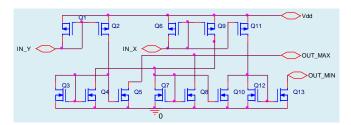

The structure of the basic relational preprocessor (BRP) of nonlinear image processing and its modified conveyor homogeneous with regular connections wave structure (MCHWS), which performs sorting and ordering of analog or digital signals and is one of the main processor nodes, are shown in Fig. 1 and were considered in more detail and described in works<sup>44-46</sup>. In the future, for simplicity, we can call this main unit the sorting unit (SU) of analog or digital signals, the specifics and implementation features of which depend on the type and form of signal representation. The work considered analog processors based on the SU, consisting of a conveyor of layers of selector-rank disjunctive-conjunctive elements (SRDCE). Modified wave structure on the basis of selector-rank disjunctive - conjunctive elements (SRDCE) using the continuous logic base analog cell with many ordered outputs. Comparative analysis of structures of ranging of analog signals (SRAS) by traditional approaches done by us shows the wave structures require less of equipment, along with other advantages (regularity, homogeneity, base cells only of 2 forms and 2 CLFs). This winning is especially and is increased at growth of number of variables n. Therefore our approach oriented to wave structure is special important at considerable n and provides integration at the requirement of multi-channeling of such devices. From other side at time-pulse coding of the element min and max CL variables (TPCV) is taken to implementation of the operations "AND" and "OR" of two-valued logic. This allows you to use only the simplest two-input AND elements and two-input OR elements for SRDCE to implement time-pulse coding of CL-variables<sup>44</sup>. In Fig. 2 shows an SRDCE circuit that is known and modified to better match currents in and out. The cell circuits of only 13 CMOS transistors, and adding 4 or 6 transistors to them, which compare the currents, it is easy to get a digital potential output of the comparator. The SRDCE as base cell executing organization of two analog optical signals that in fact is two photocurrents was designed and simulated 45, 47. The results 45 of operation of such cell are following: range of the input photocurrents 0.1÷40μA, supply voltage is 1.8÷3.3V, duration of fronts 20÷100ns, total delays no more than 200ns. Such cells are enough simple (only 13 transistors). At complication they can be more high exactness. As can be seen from Fig. 1, the well-known wave structure 44, 45 has (n-1) layers consisting of completely identical base cells, the number of which is determined by

rounding to integer  $\{n/2\}$ , where n is the number of input variables. If this number is an even number, for example, n = 6, then in each of the five layers there will be 3 basic cells, and there will be 15 of them in total (Fig. 1). For n = 4, there will be 6 base cells in all three layers. Note that for more homogeneity and regularity of bonds in the structure, it is advisable to choose n even. Therefore, for image processing, even with a minimum window size of 3x3, it is necessary to make a structure of 45 basic cells, since: (10/2)x(10-1) = 45. It can be shown that when introducing the tenth input as a control (with the value of the lower or upper boundary of the range of processed signals), the number of necessary permutations for ordering nine signals from the pixels of the current window decreases to 8, which means that the number of layers can be as little as 8. But all the same time, the number of all cells for the 3x3 window will decrease only to 40. Already with a window of 7x7, you will need ((49+1)/2)x(49-1) = 25x48 = 1200 cells, which greatly complicates the structure. In addition, due to the increase in the number of layers, the delay time of signals and errors due to their accumulation also increase. A supporting example is the following.

Fig. 1. Structure (left) of BRP with N inputs and output; SU based on MCHWS (right) for π =6 (SU have n-1=5 layers consisting of completely identical base cells SRDCE

Fig. 2 The modified continuous logic base analog cell for wave sorting structure: Selector-rank disjunctive - conjunctive element based on current mirrors with two inputs and two outputs

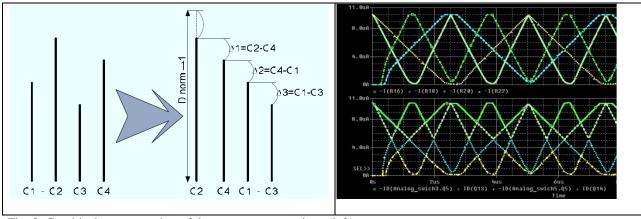

The 4-input sorting structure of analog signals using of 6 the modified CL BCs based on two-input and two-output SRDCEs is represented in work<sup>44</sup>. It executes sorting of these 4 input signals represented by photocurrents or currents. The circuit is in fact the device of order logic, calculating simultaneously all operations of the proper ranks  $r=1\div4$ . The simulation results<sup>44</sup> of such structure shown, that the structure functions correctly, although error in the levels of signals before and after do not exceed  $5\div6\%$  for currents Dmax  $=20\div40\mu A$  and  $1\div3\%$  for currents Dmax  $=5\div10\mu A$ . The multiplexer (Fig. 1) allows the control code (y1, y2, ..., yn) to choose the rank n and, accordingly, the type of required operation or function. The switch (Fig. 1) allows the control code (y1, y2, ..., yn) to select rank n and, accordingly, the type of operation required. The results of the design and simulation of the programmable relational optoelectronic time-pulse coded processor (PROTPCP)<sup>44</sup>, which, unlike the processor in Fig. 1, additionally has a block of pulse-width photo-converters-modulators<sup>47</sup> on currents mirrors showed, that for n = 8 parameters of such PROTPCP the following: processing period -  $1\div2\mu$ s,  $tdelay\Sigma\approx12\div14$ ns, 56 two-input elements of "AND" or "OR", power of the input optic signals - 0.2-200 $\mu$ W. In Fig. 3 the graphical representation of the processor operations is shown. Fig. 4 shows time diagram of PROTPCP for n=8.

Fig. 3. Graphical representation of the processor operations (left); Simulation results of the 4-input sorting structure of analog signals using of 6 the modified base analog cell based on two-input and two-output selector-rank disjunctive - conjunctive elements for small currents (right)

Fig. 4. Time diagram of PROTPCP for n=8 (shows different functions in periods)

Since such processors (Figs. 1, 3) have output signals that are ranked by value and not by difference of values, by some modification<sup>45</sup> they can be used to organize an additional calculation of the difference of signals having neighboring ranks. And the difference in signal values is also necessary for such a function as nonequivalence. Based on the operations of bounded difference and nonequivalence, a whole set of other continuous logic complex operations and functions are constructed. For example, early we can select one of n signals by rank using multiplexer. And now we can also form signals difference between max signal and next by order. So we can find signal that is proportional to difference of any two signals from ordered set. Such approach allows to formed output complement analog signals (Fig. 3). If one of reference level is 1, than difference between the reference and any of signals is the continuous logic complement of the analog signal. A block diagram of such a modified processor for four outputs, a circuit of an internal analog switch and a sub-block for calculating difference and additional analog signals are considered in work<sup>45</sup>, where it is shown that such processors can work with both analog and time-pulse-encoded signals.

# 2.2 Structure of the modified relational preprocessor (MRP) with iterative sorting node<sup>45</sup>

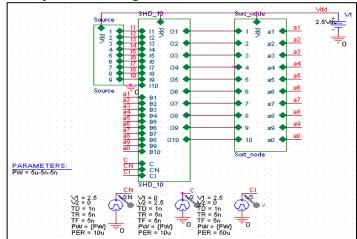

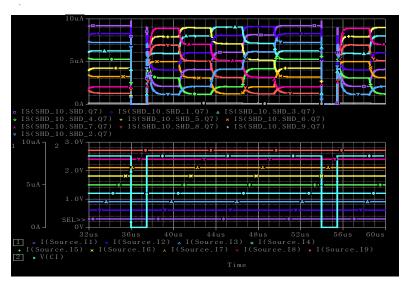

The modified iterative sorting structure based on a multichannel sampling and storage device and two linear arrays, consisting of basic continuous-logic analog cells (disjunctive-conjunctive elements of the selector rank (SRDCE) with ordered outputs) is shown in Fig. 5. Details of the structure and their base cells will be discussed in the report<sup>45</sup>. The simulation results of proposed MRP with PSpice Orcad are shown in Fig. 6, 7 for different modes of operation of the iterative sorting node. They show that for used 1.5µm CMOS transistors (Ts), the total sorting time of 10 signals (9 input information variables and one auxiliary) with permissible errors does not exceed 6÷18µs (for evaluation, we take 10µs). This time is made up of the five required clocks, but the rewriting beat in the SHD and the read beat can be different. We doubled the last one and therefore the total time was proportional to 6 cycles. The levels of input signals in the figures are indicated by different colors, which allow you to see the dynamic of transitions and the change of signal levels during exchanges, permutations. At the inputs we gave signals, ordered by their levels in the reverse order. This made it possible to more clearly demonstrate the process of ranking in which the signal with the highest level appeared at the top

output of the circuit. Let us estimate the complexity of such a sorting node. Each SHD consists of 16 Ts, there are only 10. And the two lines (layers) of basic cells with min-max operations (comparisons and exchanges in essence!) consist of 10 cells, each of which is performed on 13 Ts. Therefore, the total number of transistors will be equal to: 16x10+13x10=290. Taking into account the presence of some other auxiliary circuits: clock signal generators, a multiplexer and matching buffers; we can assume that only up to 400 transistors will be needed. Even for the fastest and most advanced algorithms and sorting schemes, the total number of comparison and exchange operations is proportional to (nlogn)x1.5 and for n=10 is about 50. Thus, taking into account that for the simulated circuit the power consumption was 2mWs and Tproc =  $10^{-5}$ s, we obtain for the simultaneous formation of ten output functions the energy efficiency estimate at the level:  $500\text{op}/(10^{-5}\text{s} \cdot 2x10^{-3}\text{ W})=25x10^9\text{ op}/\text{s} \cdot \text{W}$ . And this means that at least several hundred of them could be placed on the chip. But here the problem of interconnections will appear and the exit from it to ensure parallel inputs will be just an array of photo-detectors. Structure of multichannel 8 bit ADC (1D array 8 bit CL\_ADC) with analog signals preprocessing was described in paper32. It uses the same SHD, similar cells and iterative approaches, and this allows for additional in such processors to implement anloe-digital transformation, both before and after sorting the signals.

Fig. 5. A modified iterative sorting structure based on a multichannel sampling and storage device and two linear arrays consisting of basic continuous-logic analog cells (disjunctive-conjunctive elements of the selector rank (SRDCE) with ordered outputs).

Fig. 6. Simulation results of iterative sorting node for Vdd=2.5V, Dmax=10μA, T=18μs

Fig. 7. Simulation results of iterative sorting node for Vdd=2.5V, Dmax= $10\mu A$ , T= $18\mu s$  in the case of one ramp / falling signal and nine constants

# 3. DESIGN AND SIMULATION OF MULTIFUNCTIONAL IMAGE PROCESSING PROCESSOR (MIP) BASED ON FPGA AND USED METHOD OF PROCESSING WEIGHTING-SELECTING SIGNALS OF RANK DIFFERENCES

### 3.1 Rank differences signals weighing-selection processing method

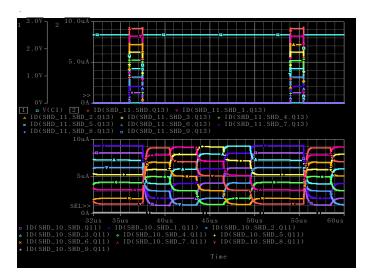

The essence of the proposed method is as follows. The signals of the selected current WAG window 3x3 in size, corresponding to the tx, ty-pixel  $Amo_{tx, ty}$  of some image, are fed to the input of the sorting node and ordered signals  $V_sor0-V_sor8$  are formed at its outputs, which are denoted as Ds (r) where r is the rank. These signals corresponding to the ranks, using the control vector Y are selected (weighed) by the switching node in accordance with the formula:

$$\mathbf{Fs}_{-}\mathbf{Am}(\mathbf{Y}) := \sum_{\mathbf{r}=0}^{9} \mathbf{Y}_{\mathbf{r}} \cdot \mathbf{Ds}(\mathbf{r})$$

Similarly, from the calculated ( $Dr0 = D - V\_sor0$ ,  $Dr1 = V\_sor0 - V\_sor1$ ,  $Dr2 = V\_sor1 - V\_sor2$ , ...  $Dr8 = V\_sor7 - V\_sor8$ ,  $Dr9 = V\_sor8$ ) rank differences, denoted by Dr (r), are selected using the similar control vector Y (weighed), if necessary, the second switching node in accordance with the formula:

$$\mathbf{F}_{-}\mathbf{Am}(\mathbf{Y}) := \sum_{\mathbf{r}=0}^{9} \mathbf{Y}_{\mathbf{r}} \cdot \mathbf{Dr}(\mathbf{r})$$

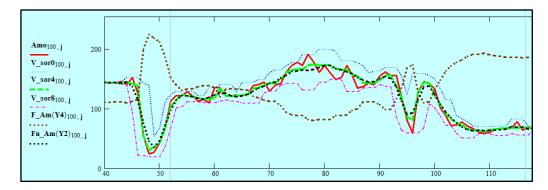

Examples of control vectors and a specific example of a window with signals to be processed, with the results obtained for it for different vectors with explanatory calculations, are shown in Fig. 8, 9. It can be seen from them that a significant number of functions, operations from window signals, including any selected rank, the difference of the selected ranks, addition to the signal, weighted sums of the selected ranks, etc. can be generated at the processor output. Thus, taking into account especially simple implementations of the operations of summation-subtraction, both for digital and analog signals, the proposed method significantly simplifies the implementation and extends the functionality, set of operations.

#### 3.2 Simulation of a multifunction processor

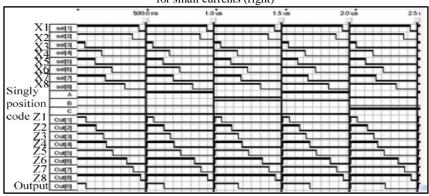

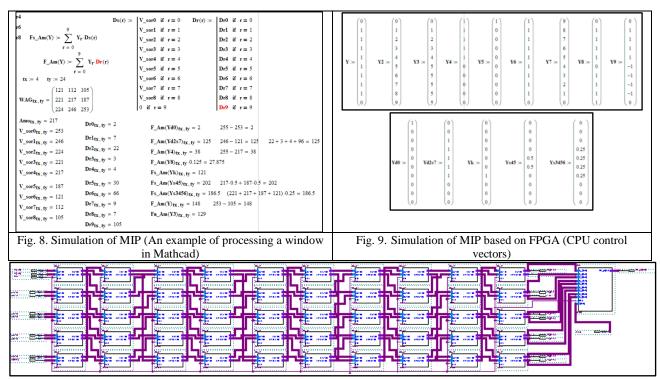

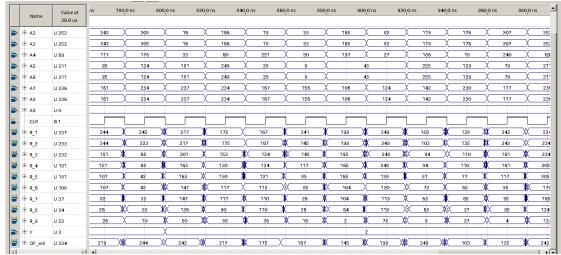

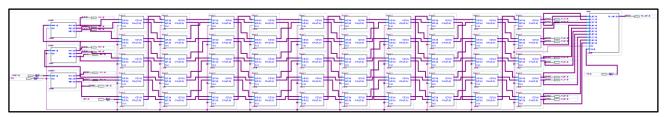

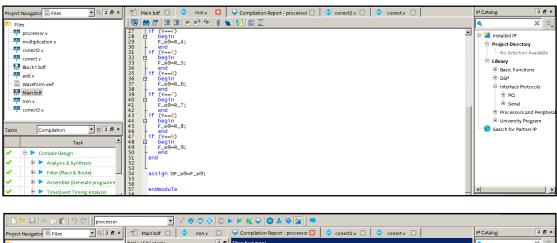

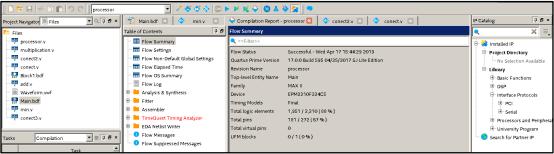

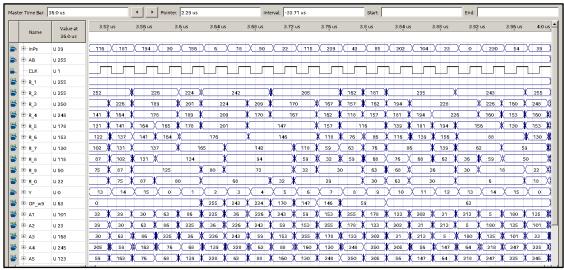

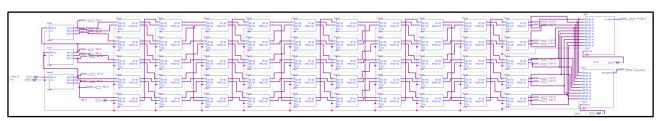

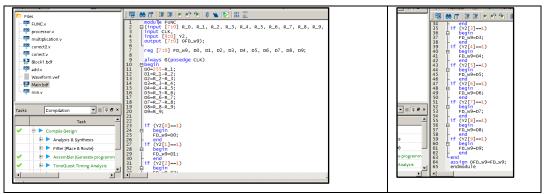

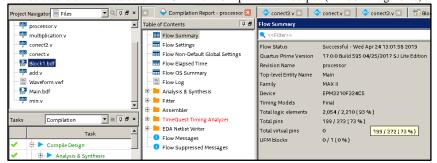

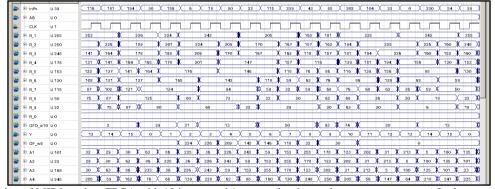

Structure of MIP based on FPGA with 10 inputs and 1 output; SU based on MCHWS consisting of layers of digital comparison switching circuits is shown in Fig. 10 and simulation results are shown in Fig. 11. Here, at first, a variant with one output and supply of all input signals in parallel is shown. For the convenience of data input, we have developed and modeled a processor circuit with register memory for fast sequential image input and automatic sequential search of processed windows. It is shown in Fig. 12. There is only one way out (ranks). The simulation results are shown in Fig. 13-20. As can be seen from Fig. 13, 17 the resources of the Altera FPGA chip EP3C16F484 Cyclone III family are not fully used in the first case, and in the second for the processor with register memory and two outputs almost completely (there is a small margin). The processing cycle in the pipelined structure of MIP and SU did not exceed 25 nanoseconds, which makes it possible to achieve an input / output rate of pixels of the processed and processed images at the level of 40 MHz. During the processing cycle, MIP essentially performs (9 \* ln9-estimates for the best algorithms!) Sorting operations and generates all the ranks and their differences, which gives, taking into account the wide variety of output functions, performance estimates of at least 109 operations per second.

Fig. 10. Structure of MIP based on FPGA with 10 inputs and 1 output; SU based on MCHWS consisting of layers of digital comparison switching circuits

Fig. 11. Simulation results of sorting node of structure of MIP based on FPGA with 10 inputs and 1 output (output switching)

Fig. 12. Structure of MIP based on FPGA with 10 inputs and 1 output with register memory

Fig. 13. Simulation of Structure of MIP based on FPGA (window fragments)

Fig. 14. Simulation results of sorting node of structure of MIP based on FPGA with 10 inputs and 1 output (issuing ranks, one switch)

Fig. 15. Structure of MIP based on FPGA with 10 inputs, 2 output and with register memory

Fig. 16. Simulation of structure of MIP based on FPGA with 10 inputs and 2 output (window fragments, unit design listings)

Fig. 17. Simulation of MIP based on FPGA with 10 inputs and 2 output (window fragments)

Fig. 18. Simulation of MIP based on FPGA with 10 inputs and 1 output (issuing ranks, two commutators) In the case of the formation of additions to the largest at the second output.

Fig. 19. A good example of processing using an MIP image line (Matcad Window): Original line (red) and received rank and other output functions.

|          | Name        | Value at<br>36.0 us | 44 us                                      | 3.48 us                 | 3.52 us   | 3.56 us | 3.6 us    | 3.64 us | 3.68 us    | 3.72 us    | 3.76 us     | 3.8 us    | 3.84 us | 3.88 us                  | 3.92 us  |

|----------|-------------|---------------------|--------------------------------------------|-------------------------|-----------|---------|-----------|---------|------------|------------|-------------|-----------|---------|--------------------------|----------|

| <u></u>  | ⊞ InPs      | U 39                | 57 X                                       | 118 X 157 X             | 116 X 181 | X 194 X | 30 X 156  | X 6 X   | 18 X 50 X  | 22 X 115   | X 239 X     | 43 X 85   | X 202 X | 104 X 23 X               | 0 X 2    |

|          | <b>⊕</b> AB | UЮ                  |                                            |                         |           |         |           |         |            |            |             |           |         |                          |          |

| in       | CLK         | U 1                 | H                                          | ΗН                      |           | 1 6     | H         | 1 🗂     | HH         | Hit        | 1 1         | НН        | 1 1     | HH                       | -        |

| out      | ® R 1       | U 255               | 17                                         |                         | 252       | 226     | X 224     |         | 42         | 205        |             | 162 181   |         | 235 🐰                    | 2.       |

| I        | -           |                     | <u>                                   </u> | 146                     | 252       | 189     | X 201     | 224     | ¥ 209 ¥    | 170        | X 167 X     | 157 1 162 | 194 🐰   | 228                      | X 22     |

| 15       | ⊕ R_2       | U 250               |                                            |                         |           |         |           |         |            |            |             | :         |         |                          |          |

| =        | ⊕ R_3       | U 248               |                                            | 122                     | 141 ( 164 | 178     | 189       | 209     | X 170 X    | 167        | 162         | 118 157   | 181     | 194 X 226                | <u> </u> |

| =        | ⊕ R_4       | U 178               | 7 X 19                                     | 07 💥 102 🦹              | 131 (141  | 164 X 1 | 65 178    | 201     | X          | 147        | 157         | 116       | 139     | 181 194                  | 156      |

| <b>₩</b> | ⊕ R_5       | U 153               | 5 6                                        | 75                      | 122 137   | 141 🗶 1 | 64        | 176     | X          | 146        | 118         | 76 86     | 116     | 139 🗱 156 🕱              | 81       |

| *        | ⊕ R_6       | U 130               | X_3                                        | 35 <b>X</b> 67 <b>X</b> | 102 131   | 137     | X 16      | i5      | 142        | 118        | <b>X</b> 59 | 63 76     | 86      | 139                      | 62       |

| 94       | ₽ R_7       | U 115               |                                            | <b>₩</b> 35 <b>₩</b>    | 87 102    | 131     | 134       | X_      | 94         | 59         | X 32 X      | 59 68     | 76      | 68 <b>X</b> 62 <b>X</b>  | 36 🗱 5   |

| *        | ⊕ R_8       | U 50                |                                            | ж                       | 75 87     | 1       | 25        | 80      | 73         | 32         | 30          | 63        | 68      | 36                       | 30       |

| 94       |             | U 22                |                                            |                         | 75        | 87 XX   | 80 X      |         | 58         | 32         | 29          | X 30      | 63      | 30                       | E        |

| *        | ⊕ R_O       | UО                  |                                            |                         |           |         |           |         |            |            |             |           |         |                          |          |

| om.      | ⊕ OFD w10   | U 88                | 46                                         | X 24                    | XX 5 X    | 62      | 11        | 12      | 15 🗶       | 39         | з )(        | 5 ( 39 )  | 5 X     | 13 🗱 34 🚶                | 2        |

| -        | ● γ         | UO                  | 10 X                                       | 11 X 12 X               | 13 X 14   | X 15 X  | 0 X 1     | X 2 X   | 3 X 4 X    | 5 X 6      | X 7 X       | 8 \chi 9  | X 10 X  | 11 X 12 X                | 13 X     |

| 944      | ⊕ OF_w9     | UO                  |                                            | 0                       |           |         |           | 224 X 2 | 26 ¥ 209 X | 145 🐰 146  | ¥ 118 ¥     | 32 🕻 3    | o X     |                          | 0        |

| 944      | ⊕-A1        | U 101               | 9 🗶 14                                     | 42 X 147 X              | 32 1 29   | 30 X 6  | 3 X 86    | 235 🗶 3 | 36 X 226 X | 243 \$ 59  | X 153 X     | 255 X 178 | 123 🗶 2 | eo2 <b>X</b> 31 <b>X</b> | 213 🗶 5  |

| 1-       | ⊕- A2       | U 23                |                                            | 47 X 32 X               | 29 30     |         | 36 235    | :_      | 25 1 243 1 | 59 153     | X 255 X     | 178 1 123 |         | 31 🗶 213 🗶               | 5 1 18   |

| out.     | -           |                     | 7 1 3                                      |                         |           |         |           | =:=     |            | 153 \$ 255 |             | 123 0 202 |         |                          | 180 🕻 13 |

| -        | ● A3        | U 168               |                                            |                         | 30 ) 63   |         | 35 36     |         |            |            |             |           |         |                          |          |

| *        | ± A4        | U 245               | 12 1 9                                     | 94 🗱 170 🛣              | 205 59    | 162     | 76 X 68 X | 139 2   | 28 🗱 62 🛣  | 88 🗱 160   | 130         | 248 250   | 205     | 56 🖟 147 🦹               | 64 2'    |

Fig. 20. Simulation results of sorting node of structure of MIP based on FPGA with 10 inputs and 1 output (issuing ranks, two switches) In case of formation of a difference of ranks r2-r3

#### CONCLUSIONS

We proposed a new iterative process of sorting an array of signals, which differs from the known structures of sorting signals by uniformity, versatility, which allows direct and inverse sorting of an array of analog or digital signals. The basic elements of the proposed sorting unit (SU) are simple relational nodes. Such elements can be implemented on a different element basis, including, on devices for selecting a maximum or minimum of two analog or digital signals. We offered implementation of homogeneous SU on CL BCs, consisting of two layers and a multichannel SHDs and FPGA. Nine signals corresponding to a selection window of a matrix sensor are fed to this structure, we sort them in five iterative steps, and at the output we receive the signals sorted by the rank, which, using the code controlled programmable multiplexer, generates an output signal, corresponding to the selected rank. We evaluated the technical parameters of such a relational preprocessor. The CL BC on current mirrors (CM) consist of no more than 20 CMOS transistors, the total power consumption of the sorting node on 10 cells is 2mW, the supply voltage is 1.8÷3.3V, the range of an input current is 0.1÷24µA, the conversion cycle is 10µs. Such SU for creating picture type image processors (IP) with matrix parallel inputs-outputs have a number of advantages: high speed and reliability, simplicity, small power consumption, high integration level. The inclusion of an iterative node for sorting signals into a modified nonlinear IP structure makes it possible to significantly simplify its design and increase the functional capabilities of such IP. The simulation results confirm the proposed approaches to the design of SUs of analog signals of the iterative type, which simplify the complexity of the nodes by an order of magnitude, ensuring their uniformity, regularity and simplicity of scaling. The power consumption of the IPs does not exceed 2mW, the response and processing times are 10µs and can be less by an order of magnitude, the supply voltage is 1.8÷3.3V, and the operating currents are optimally in the range of 10÷20μA. The energy efficiency of the proposed preprocessor with the iterative SU is 25x10<sup>9</sup> op / s · W, which corresponds to the best technical solutions. In the work we are shown, that after sorting or comparative analysis of signals by levels of selected window of image, a promising opportunity appears to implement MIPs with enhanced functionality using the new method of weighting-selecting rank differences of signals. The essence of the method is that by composing the differences of the signals ordered by rank and the upper level of their range, we can simultaneously form several resulting output signals, choosing the necessary difference signals from their set according to the control commands and weighing them additionally before the summation. We are shown that using this approach of processing the current window signals significantly expands the set of operations and functions for filtering images, simplifying hardware implementation of MIP, especially for analog and mixed technologies. We determined set of basic possible executable instruction-functions by processors based on such a proposed method, presenting the simulation results. We show the results of design and modeling the proposed new FPGA-implementations of MIP. Simulation results show that processing time in such circuits does not exceed 25 nanoseconds. Circuits are simple, have low supply voltage (2.5 V), low power consumption (50mW), digital accuracy. Calculations show that when using an Altera FPGA chip EP3C16F484 Cyclone III family, it is possible to implement MIP with register memory for image size of 64\*64 and window 3\*3 in the one chip. For the chip for 2.5V and clock frequency 200MHz the power consumption will be at the level of 200mW, and the calculation time for pixel of filters will be at the level of 25ns.

### REFERENCES

- [1] Fey, D., "Architecture and technologies for an optoelectronic VLSI," Optic 112(7), 274-282 (2001).

- [2] Lei Yi, Guangbao Shan, Song Liu, Chengmin Xie, High-performance processor design based on 3D on-chip cache, Microprocessors and Microsystems, Volume 47, 2016, Pages 486-490, ISSN 0141-9331, http://dx.doi.org/10.1016/j.micpro.2016.07.009.

- [3] Krasilenko, V. G., Lazarev, A., Grabovlyak, S., "Design and simulation of a multiport neural network heteroassociative memory for optical pattern recognitions," Proc. of SPIE Vol. 8398, 83980N-1 (2012).

- [4] Mori, M., Yatagai, T., "Optical learning neural networks with two dimensional structures," Proc. SPIE 3402, 226-232 (1997).

- [5] Krasilenko, V., Nikolskyy, A., Zaitsev A., Voloshin V., "Optical pattern recognition algorithms on neural-logic equivalent models and demonstration of their prospects and possible implementations," Proc. SPIE 4387, 247 –260 (2001).

- [6] Krasilenko, V. G., Nikolskyy, A. I., Lazarev, A. A. [Design and Simulation of Time-Pulse Coded Optoelectronic Neural Elements and Devices, Optoelectronic Devices and Properties], InTech (2011). ISBN: 978-953-307-204-3, DOI: 10.5772/16175. Available from: <a href="http://www.intechopen.com/books/optoelectronic-devices-andproperties/design-and-simulation-of-time-pulse-coded-optoelectronic-neural-elements-and-devices">http://www.intechopen.com/books/optoelectronic-devices-andproperties/design-and-simulation-of-time-pulse-coded-optoelectronic-neural-elements-and-devices</a>

- [7] Krasilenko, V. G., Nikolskyy, A. I., Lazarev, A. A., [Design and Modeling of Optoelectronic Photocurrent Reconfigurable (OPR) Multifunctional Logic Devices (MFLD) as the Universal Circuitry Basis for Advanced Parallel High- Performance Processing, Optoelectronics Advanced Materials and Devices], InTech (2013). ISBN: 978-953-51-0922-8, DOI: 10.5772/54540.

- [8] Krasilenko, V. G., Nikolskyy, A. I., Lazarev, A. A., "Designing and simulation smart multifunctional continuous logic device as a basic cell of advanced high-performance sensor systems with MIMO-structure," in Photonics, Devices, and Systems VI, Dagmar Senderáková; Petr Páta; Pavel Tománek, Editors, Proc. SPIE 9450, 94500N (2015).

- [9] Guilfoyle, P., McCallum, D., "High-speed low-energy digital optical processors," Opt. Eng. 35(2), 436-442 (1996).

- [10] Krasilenko, V.G., Bardachenko, V.F., Nikolsky, A.I., Lazarev, A.A., Kolesnytsky, O.K. "Design of optoelectronic scalar-relation vector processors with time-pulse coding," Proc. SPIE 5813, 333-341 (2005).

- [11] Krasilenko, V., Ogorodnik, K., Nikolskyy, A., Dubchak, V., "Family of optoelectronic photocurrent reconfigurable universal (or multifunctional) logical elements (OPR ULE) on the basis of continuous logic operations (CLO) and current mirrors (CM), "Proc. SPIE, 8001, (2011).

- [12] Krasilenko, V. G., Nikolskyy, A. I., Lazarev, A. A., "Simulation of reconfigurable multifunctional continuous logic devices as advanced components of the next generation high-performance MIMO-systems for the processing and interconnection," Proc. SPIE 9009, 90090R (2014).

- [13] Krasilenko, V. G., Nikolskyy, A. I., Lazarev, A. A., "Multichannel serial-parallel analog-to-digital converters based on current mirrors for multi-sensor systems", Proc. SPIE 8550, Optical Systems Design 2012, 855022 (2013); doi:10.1117/12.2001703.

- [14] Volgin, L.I., Mishin, V.A., "Is the future digital or analog?," Information technologies in electric power industry: Cheboksary: RESCNIT, 86-89, (1998).

- [15] Volgin, L.I., Mishin, V.A., "Nobody will think for us: Retrospective review and ontological comprehension of artificial intelligence," Sensors and Systems, Vol. 4 (8), 43-48 (1999).

- [16] Volgin, L.I., Mishin, V.A., "Ontological aspects of artificial intelligence," Vestnik UlPU, Vol. 4 (8), 13-19 (1999).

- [17] Odintsov, B.Y., Dick, V.V., "Syntax of knowledge models of intelligent systems," Instruments and Control Systems, Vol. 1, 15-17 (1998).

- [18] Lukasiewicz, J., "Elementy logiki matematycznej," Warsawa, (1929).

- [19] Levin, V.I., 'Continuous logic, its generalization and application," Automatica and telemechanica, N8, 3-22, (1990).

- [20] Shimbirev, P.N., "Hybrid continuous logic devices," Moscow, Energoatomizdat, 174p., (1990).

- [21] Volgin, L.I., "AM-algebra and its application," Ulyanovsk, UISTU, 52p., (1997).

- [22] Volgin, L.I., "Predicate Algebra of Choice and Its Modification (Fundamentals of the Theory and Elemental Basis), "Experience, Results, Problems: Increasing the Competitiveness of Electronic Equipment. Collection of articles, Tallinn, Valgus, Vol. 4, 64-104, (1986).

- [23] Krasilenko, V. G., Saletsky, F. M., Yatskovsky, V. I., Konate, K., "Continuous logic equivalence models of Hamming neural network architectures with adaptive-correlated weighting," Proc. SPIE 3402, 398 408 (1998).

- [24] V. LeCun, Y., Bengio, Y., "Convolutional networks for images, speech, and time-series," In M. A. Arbib, editor, The Handbook of Brain Theory and Neural Networks. MIT Press, 1995.

- [25] V. Shafiee, A., et al., "ISAAC: A Convolutional Neural Network Accelerator with In-Situ Analog Arithmetic in Crossbars," 2016 ACM/IEEE 43rd Annual International Symposium on Computer Architecture (ISCA), Seoul, 2016, pp. 14-26. doi: 10.1109/ISCA.2016.12.

- [26] Krasilenko, V.G., Lazarev A.A., Nikitovich D.V., "Modeling and possible implementation of self-learning equivalence-convolutional neural structures for auto-encoding-decoding and clusterization of images," Proceedings of SPIE Vol. 10453, 104532N (2017).

- [27] Krasilenko, V. G., Lazarev, A. A., Nikitovich, D. V., "Design and simulation of optoelectronic neuron equivalentors as hardware accelerators of self-learning equivalent convolutional neural structures (SLECNS)," Proceedings of SPIE Vol. 10689, 106890C (2018).

- [28] Sidorov, V.I., Yaroslavsky, L.P., "Additive method for image processing," Moscow, Nauka, 243p. (1988).

- [29] Pozin, N.V., "Simulation of neural structures," Moscow, Nauka, 264p. (1970).

- [30] Krasilenko, V. G., Nikolskyy, A. I., Krasilenko, O. V., Nikolska, M. A., "Continuously logical complementary: dual equivalently analog-to-digital converters for the optical systems," Proc. SPIE 8001-30, (2011).

- [31] Krasilenko, V. G., Nikolskyy, A. I., Lazarev, A. A., Krasilenko, O. V., Krasilenko, I. A., "Simulation of continuously logical ADC (CL ADC) of photocurrents as a basic cell of image processor and multichannel optical sensor systems", Proceedings of SPIE Vol. 8774, 877414 (2013).

- [32] Krasilenko, V. G., Lazarev, A. A., Nikitovich, D. V., "Simulation of continuously logical base cells (CL BC) with advanced functions for analog-to-digital converters and image processors," Proc. SPIE 10438, 104380K (2017)

- [33] Musa, P., Sudiro, S.A., Wibowo, E.P., Harmanto, S., Paindavoine, M. (2012), "Design and implementation of non-linear image processing functions for CMOS image sensor", Optoelectronic Imaging and Multimedia Technology II, Proc. of SPIE Vol. 8558 <a href="http://spie.org/Publications/Proceedings/Paper/10.1117/12.2000538">http://spie.org/Publications/Proceedings/Paper/10.1117/12.2000538</a>.

- [34] Development and simulation of soft morphological operators for a field programmable gate array Andrew J. Tickle Paul K. Harvey Jeremy S. Smith Q. Henry Wu Journal of Electronic Imaging 22(2), 023034 (Apr–Jun 2013) 023034-1-023034-15 2013 SPIE and IS&T [DOI: 10.1117/1.JEI.22.2.023034].

- [35] Tickle, A. J., Harvey, P. K., Smith, J. S., "Applications of a morphological scene change detector (MSCD) for visual leak and failure identification in process and chemical engineering," Proc. SPIE 7833, 78330W (2010).

- [36] Tickle, A. J., "Applications of morphological operators on field programmable gate arrays," Doctoral Thesis, Univ. of Liverpool, pp. 326–332 (2009).

- [37] Image enhancement and segmentation using weighted morphological connected slope filters Jorge D. Mendiola-Santibañez Iván R. Terol-Villalobos Journal of Electronic Imaging 22(2), 023022 (Apr–Jun 2013) DOI. [DOI: 10.1117/1.JEI.22.2.023022].

- [38] D. E. Knuth, The Art of Computer Programming. Reading, MA, USA: Addison-Wesley, Mar. 2011.

- [39] Y. Bang and S. Q. Zheng, "A simple and efficient VLSI sorting architecture," in Proc. 37th Midwest Symp. Circuits Syst., vol. 1. 1994, pp. 70–73.

- [40] T. Leighton, Y. Ma, and C. G. Plaxton, "Breaking the\_(n log2n) barrier for sorting with faults," *J. Comput. Syst. Sci.*, vol. 54, no. 2, pp. 265–304, 1997.

- [41] W. Jianping, Y. Yutang, L. Lin, H. Bingquan, and G. Tao, "Highspeed FPGA-based SOPC application for currency sorting system," in *Proc. 10th Int. Conf. Electron. Meas. Instrum. (ICEMI)*, Aug. 2011, pp. 85–89.

- [42] J. L. Bentley and R. Sedgewick, "Fast algorithms for sorting and searching strings," in Proc. 8th Annu. ACM-SIAM Symp. Discrete Algorithms (SODA), Jan. 1997, pp. 360–369.

- [43] V. Kundeti and S. Rajasekaran, "Efficient out-of-core sorting algorithms for the parallel disks model," J. Parallel Distrib. Comput., vol. 71, no. 11, pp. 1427–1433, 2011.

- [44] Krasilenko, V. G., Bardachenko, V. F., Nikolsky, A. I., Lazarev, A. A., "Programmed optoelectronic time-pulse coded relational processor as base element for sorting neural networks," Proc. SPIE 6576, 657610 (2007).

- [45] Krasilenko, V. G., Nikolskyy, A. I., Lazarev, A. A., Lazareva, M.V. "Design and simulation of programmable relational optoelectronic time-pulse coded processors as base elements for sorting neural networks", Proceedings of SPIE Vol. 7723, 77231G (2010).

- [46] Krasilenko, V.G., Lazarev A.A., Nikitovich D.V., "Design and simulation of image nonlinear processing relational preprocessor based on iterational sorting node," Proc. SPIE 11028, Optical Sensors 2019, 110282X (11 April 2019); doi: 10.1117/12.2524114

- [47] Krasilenko, V.G., Nikolsky, A.I., Lazarev, A.A., Michalnichenko, N.N. "Smart time-pulse coding photoconverters as basic components 2D-array logic devices for advanced neural networks and optical computers," Proc. SPIE 5439, 198-209 (2004).